(Full video not showing? view it here)

Key Takeaways

- PQShield has developed a fully functional NIST-ready PQC silicon test chip

- Built to accelerate compliance with emerging post-quantum standards

- Enables real-world evaluation of performance, power, and SCA countermeasures

- Supports firmware updates for evolving standards and algorithms

- Demonstrates practical deployment of quantum safe asymmetric encryption in hardware

PQShield Builds NIST-Ready PQC in Silicon

(Full video not showing? View it here)

With the release of the first three NIST PQC standards, the world of post-quantum cryptography (PQC) is rapidly shifting from a focus on preparation, to a much sharper focus on compliance. As organisations prepare for quantum safe asymmetric encryption, adoption is no longer optional.

“For the first time, everyone has to look at how they adopt,” explains Graeme Hickey, PQShield’s VP, Engineering. “It’s no longer a PoC or a research item; it’s now something that’s a must-do, and I think we’re going to see an increase in interest from industry and companies looking to work out how to solve the post-quantum problem.”

Many of these first adopters will of course be at the root of the supply chain, such as semiconductor manufacturers who provide the boards and systems other companies rely on. Having PQC in these components is critical for the rest of the supply chain, particularly as quantum safe asymmetric encryption becomes a compliance requirement.

It is clear already from many of our customers in this sector that the quantum shift — from preparation to compliance — is already on.

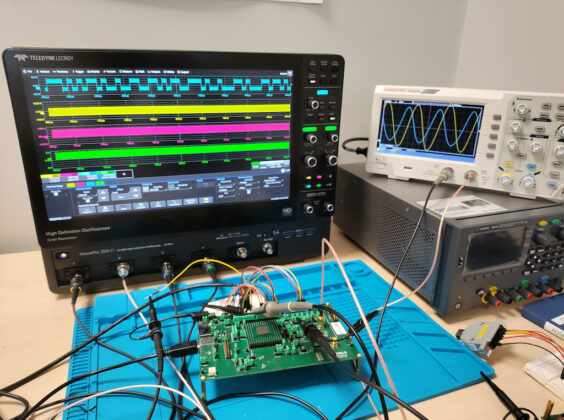

That’s one of the reasons why PQShield are excited to announce that we’ve designed and built our own fully functional PQC silicon test chip.

A PQC-Compliant Silicon Test Chip

PQShield believes this is the first ever PQC-compliant silicon chip. It’s fully loaded with all the power of our PQPlatform IP, specifically focused on platform security for SoC semiconductor vendors with implementation security in mind. These are linked below:

By building our own ASIC, we can now demonstrate and test the IP in the way that a customer will use it. We’re able to evaluate its operation in real detail, looking at how to be compliant against the standards, and perform security testing in a way that would be practically difficult on a customer product deployed in the field.

Performance and Side-Channel Validation in Real Silicon

In addition, the test chip gives us the ability to deep-dive into areas like power utilization, performance, and critically, the efficiency of Side Channel Analysis (SCA) countermeasures. As Graeme explains:

“It’s much easier to do this type of evaluation on a real product, as opposed to a pre-silicon simulation, or using FGPA, and it’s far more reflective of what a final product would look like.”

Flexible, Future-Ready Architecture

Another benefit is the test chip’s flexibility. The chip itself is a hardware/software co-design IP, and it allows us to update the firmware directly in order to modify the algorithms it supports.

Designed for Standards Evolution

That means that it can be configured to be more standards-compliant in future, or perhaps even more secure from side-channel attack as analysis continues.

The test chip has completely programmable firmware — a feature that will certainly be useful as NIST standardization continues, especially with the outstanding Round 4 KEMs, as well the on-ramp for new, wider digital signature schemes, such as our own side-channel secure, masking-friendly RACCOON scheme.

RACCOON has been specifically included in our silicon and this is likely to be the first time there has ever been an implementation in silicon that can actually be tested.

Supporting Compliance as the Quantum Shift Continues

As the quantum shift continues, the focus on compliance with the NIST standards will sharpen, particularly as industry regulation follows.

Our engineering and research teams have worked hard to ensure that PQShield has a tool that can allow us to test, evaluate and configure real-world post-quantum cryptography, keeping us all one step ahead of the quantum threat.

For organisations preparing for quantum safe asymmetric encryption, this represents a practical and silicon-proven path to compliance.

Review PQShield’s products and speak to PQShield about your silicon needs for quantum safe asymmetric encryption today.

Frequently Asked Questions

What is quantum safe asymmetric encryption?

Quantum safe asymmetric encryption refers to cryptographic algorithms designed to resist attacks from quantum computers, particularly those capable of breaking classical public key cryptography.

Why is NIST standardisation important for quantum safe asymmetric encryption?

NIST standardisation provides validated, interoperable algorithms that organisations can adopt with confidence. It ensures compliance readiness and supports secure deployment at scale.

How does PQShield support semiconductor vendors?

PQShield provides silicon-proven IP, including its PQPlatform suite and test chips, enabling semiconductor vendors to embed post-quantum security directly into SoCs and hardware components.

What makes PQShield’s silicon test chip unique?

The chip enables real-world testing of power, performance, compliance, and side-channel resilience. It includes programmable firmware for adapting to evolving standards and integrates advanced schemes like RACCOON.

How can organisations start implementing quantum safe asymmetric encryption?

Organisations should begin by assessing their cryptographic footprint and engaging with experienced providers like PQShield to integrate NIST-ready, silicon-optimised solutions aligned with future regulatory requirements.